# BUILDING KNOWLEDGE SYSTEMS IN A-PROLOG MONICA DE LIMA NOGUEIRA

Computer Science Department

| APPROVED:                     |

|-------------------------------|

| Michael Gelfond, Ph.D., Chair |

| Chitta Baral, Ph.D.           |

| Vladik Kreinovich, Ph.D.      |

| Luc Longpré, Ph.D.            |

| Enrico Pontelli, Ph.D.        |

Charles H. Ambler, Ph.D. Dean of the Graduate School

#### BUILDING KNOWLEDGE SYSTEMS IN A-PROLOG

by

### MONICA DE LIMA NOGUEIRA

### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at El Paso

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

Computer Science Department  $\begin{tabular}{ll} THE UNIVERSITY OF TEXAS AT EL PASO \\ MAY 2003 \end{tabular}$

#### THE UNIVERSITY OF TEXAS AT EL PASO

Date: **May 2003**

Author: MONICA DE LIMA NOGUEIRA

Title: Building Knowledge Systems in A-Prolog

Department: Computer Science

Degree: **Ph.D.** Convocation: **May** Year: **2003**

Permission is herewith granted to The University of Texas at El Paso to circulate and to have copied for non-commercial purposes, at its discretion, the above title upon the request of individuals or institutions.

Signature of Author

THE AUTHOR RESERVES OTHER PUBLICATION RIGHTS, AND NEITHER THE THESIS NOR EXTENSIVE EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT THE AUTHOR'S WRITTEN PERMISSION.

THE AUTHOR ATTESTS THAT PERMISSION HAS BEEN OBTAINED FOR THE USE OF ANY COPYRIGHTED MATERIAL APPEARING IN THIS THESIS (OTHER THAN BRIEF EXCERPTS REQUIRING ONLY PROPER ACKNOWLEDGEMENT IN SCHOLARLY WRITING) AND THAT ALL SUCH USE IS CLEARLY ACKNOWLEDGED.

To my children,

Heloisa, Marcus Vinicius, and Daniela,

$with\ love.$

## Acknowledgements

"As we express our gratitude, we must never forget that the highest appreciation is not to utter words, but to live by them."

John F. Kennedy (1917-1963)

I am blessed to have always had the opportunity to meet extraordinary people. People who have taught me a great deal. I am also blessed to have the support and love from family and friends no matter where in the world I happened to be. Therefore, I am lucky to have a long list of people to thank for the help they gave me to complete my studies.

I am especially indebted to my advisor Michael Gelfond for sharing his knowledge and his vision of science, philosophy, mathematics, politics, religion, literature, beauty, history, and innumerous other subjects. From him I learned about logic and the validity of arguments, both of which have changed the way I think and interact with other people. Without his help and encouragement, this work would not have been successful.

I am grateful for what I learned in the many classes I took with Chitta Baral, Vladik Kreinovich, and Luc Longpré, and for their support and attention to detail when reviewing this dissertation as my committee members. I want to thank my external committee member Enrico Pontelli for his helpful comments and the many suggestions he made to improve this text. I also had the help and support of Son Cao Tran who reviewed an earlier version of the mathematical proofs presented here and pointed out many of the mistakes I needed to correct. I especially need to thank Michael, Chitta, Enrico, and Son for making the effort of coming to El Paso on such short notice at the end of the semester to attend my dissertation defense; and Luc and Vladik for making special arrangements regarding their final exams so they could be present. Luc was also thoughtful enough as to write down his observations about how I can improve my presentation of this work, for which I thank him.

As a demanding client who is very particular about details, I need to thank Marcello Balduccini twice for the many hours he worked in the implementation of the graphical interfaces for the A-Circuit and the USA-Advisor systems that I designed. It was a pleasure working with him on these projects, and I greatly benefited from our discussions.

I am also thankful to other graduate students (past and present) from the Knowledge Representation Laboratory (KRLab), previously at The University of Texas at El Paso (UTEP) and currently at Texas Tech University (TTU). I particularly wish to thank Veena Mellarkod, Joel Galloway, and Mary Heidt who allowed me to participate in their work and to learn from it.

For the last three years I have been a constant visitor at the KRLab at TTU. I wish to thank Daniel Cooke and his staff for making the Computer Science Department at TTU an extension of the one at UTEP; I always felt welcome there and found it a friendly place where I could continue my work. During this time, I was also constantly a guest at the Gelfonds' home and wish to express my gratitude to Lara Gelfond for her gracious hospitality and friendship. I especially wish to thank Lara, Gregory, and Michael for those extra working hours stolen from their family time together.

Since I started working with the SMODELS and the DVL inference engines, I have had the help and support of their development teams, which I would like to thank: Illka Niemelä, Patrik Simons, and Tommi Syrjänen for SMODELS, and Nicola Leone, Wolfgang Faber, and Gerald Pfeifer for DLV.

I am also very fortunate because I participated and learned from many technical discussions and exchanges of ideas in the Texas Action Group (TAG) organized by Vladimir Lifschitz and Michael Gelfond. I wish to thank them both for creating this forum and encouraging researchers and students alike to be part of it. I particularly want to thank Vladimir, Michael, and the TAG members for the ideas they have shared with me. This group includes Yuliya Babovich, Marcello Balduccini, Chitta Baral, Pedro Cabalar, Jonathan Campbell, Esra Erdem, Wolfgang Faber, Paolo Ferraris, Alfredo Gabaldon, Joel Galloway, Mary Heidt, Vladik Kreinovich, Jooyhung Lee, Sheila McIlraith, Veena Mellarkod, Ramon Otero, Gerald Pfeifer, Enrico Pontelli, Tommi Syrjänen, Son Cao Tran, Le-Chi Tuan, Hudson Turner, and many others. I would like to thank the United Space Alliance (USA) company for providing partial financial support for this research through several research grants and contracts. In

addition, I would like to thank Matthew Barry from USA and Richard Watson from

TTU for answering questions about the Reaction Control System of the space shuttle

which helped the development of this work. My research was also partially supported

by a scholarship from the National Science Foundation for which I am very grateful.

There are too many friends who helped me through my studies and for whom I

am thankful. Of all these friends, I wish to single out Nelly Delgado and Frank

Fernandez for their constant support and unconditional dependability. During the

busy preparations for my dissertation, they always made sure the little things got

done. They will always have my gratitude and my friendship.

Finally I wish to express my utmost gratitude to my parents for their love and will-

ingness to be my support team at home, supervising my children and my household

for weeks and months at a time while my husband and I were many miles away. I

would never be able to complete my studies without their help. I want to thank my

husband for his support and for believing I could finish this work even when I did

not. Lastly, I want to thank my children for understanding and valuing my desire

to become a better person through my studies, even if it meant I would be away for

long periods of time. I am sure this hardship brought us closer together and was a

worthwhile lesson that will always stay with us.

Monica de Lima Nogueira

The University of Texas at El Paso

May 2003

### Abstract

This work is written in the context of the logic-based approach to Artificial Intelligence (AI) proposed by John McCarthy in 1959 [134]. According to this approach an agent should have knowledge of its world and its goals, and the ability to use this knowledge to infer its course of action. This logic-based method suggests that a mathematical model of an agent should contain: a formal language capable of expressing commonsense knowledge about the world, a precise characterization of valid conclusions which can be derived from theories stated in this language, and a means which will allow the agent to arrive at these conclusions.

The purpose of this dissertation is to investigate the applicability of one such language, A-Prolog [71, 73], for the development of medium-size knowledge-intensive systems. A-Prolog is a declarative logic programming language based on stable models/answer sets semantics of logic programs [74, 75]. It allows the representation of defaults and several interesting aspects of reasoning about actions and their effects. There is a recently developed methodology of representing knowledge in A-Prolog, and there are also rather efficient inference engines associated with the language. Our goal

was to test this methodology and these inference engines on sizeable engineering applications.

In this dissertation, we developed two such applications. The first is a small system, designed as a classroom tool for teaching digital circuits, which allows the functional and behavioral representation of these circuits at the gate-level of abstraction. The second is a substantially larger application - the implementation of a decision support system for the space shuttle's flight controllers. This work involved the representation of a substantial amount of knowledge about the shuttle as well as the execution of complex planning (and other reasoning) tasks. The project was successful, and the system is now in the hands of United Space Alliance (USA), the company responsible for overseeing the operation of the space shuttle.

This dissertation describes the design and implementation of these systems and discusses some lessons derived from this experience. We believe that the lessons can be of interest to AI researchers working in the areas of knowledge representation, nonmonotonic reasoning, and planning, as well as to software engineers involved in the construction of knowledge-intensive systems.

# Table of Contents

| A            | ckno         | wledgements                                | v           |

|--------------|--------------|--------------------------------------------|-------------|

| $\mathbf{A}$ | bstra        | $\operatorname{\mathbf{ct}}$               | ix          |

| Li           | st of        | Tables                                     | xiv         |

| Li           | st of        | Figures                                    | <b>xv</b> i |

| 1            | Intr         | oduction                                   | 1           |

|              | 1.1          | Logic Approach to AI                       | 2           |

|              | 1.2          | Goals and Contributions of this work       | 21          |

|              | 1.3          | Organization of the dissertation           | 24          |

| <b>2</b>     | $Th\epsilon$ | A-Prolog Language                          | <b>2</b> 5  |

|              | 2.1          | Syntax                                     | 25          |

|              | 2.2          | Semantics                                  | 27          |

| 3            | Dig          | ital Circuits in A-Prolog                  | 36          |

|              | 3.1          | Digital Circuits in Electrical Engineering | 36          |

5.2

5.3

|              |                  |                                             | xiii |

|--------------|------------------|---------------------------------------------|------|

|              | 5.4              | USA-Advisor System's Design                 | 128  |

|              |                  | 5.4.1 Plumbing module                       | 130  |

|              |                  | 5.4.2 Valve control module                  | 139  |

|              |                  | 5.4.3 Circuit theory module                 | 160  |

|              |                  | 5.4.4 Planning module                       | 174  |

|              | 5.5              | The Basic Planner                           | 175  |

|              | 5.6              | Smart Planner: adding the control knowledge | 179  |

|              | 5.7              | Experimental Results for the USA-Advisor    | 186  |

|              | 5.8              | Summary                                     | 198  |

| 6            | Con              | onclusions                                  |      |

|              | 6.1              | Lessons Learned                             | 204  |

|              | 6.2              | Future Work                                 | 205  |

| A            | RCS              | S Experiments' Results                      | 210  |

| Bibliography |                  | 242                                         |      |

| Cı           | Curriculum Vitae |                                             |      |

## List of Tables

| 3.1  | Definition of behavior of basic gates                                     | 41  |

|------|---------------------------------------------------------------------------|-----|

| 5.1  | (a) Tri-State gate. (b) Negated Input Logic AND gate                      | 163 |

| 5.2  | Definition of the behavior of a Time Delay (of 1 sec) gate                | 163 |

| 5.3  | Overall results for 2000 RCS experiments                                  | 198 |

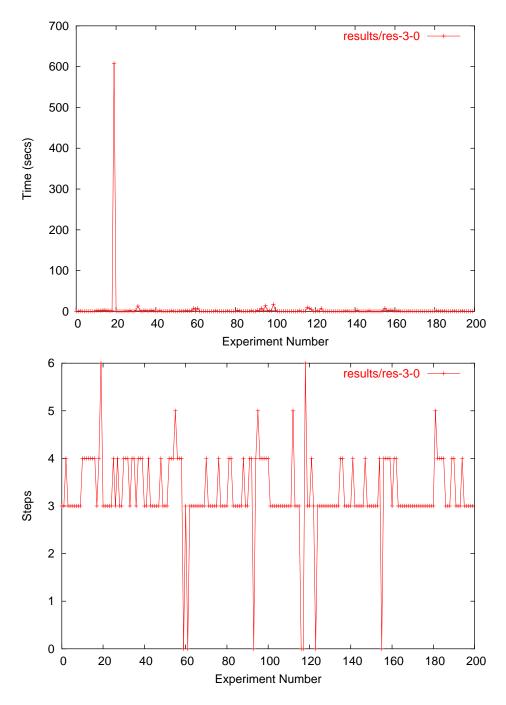

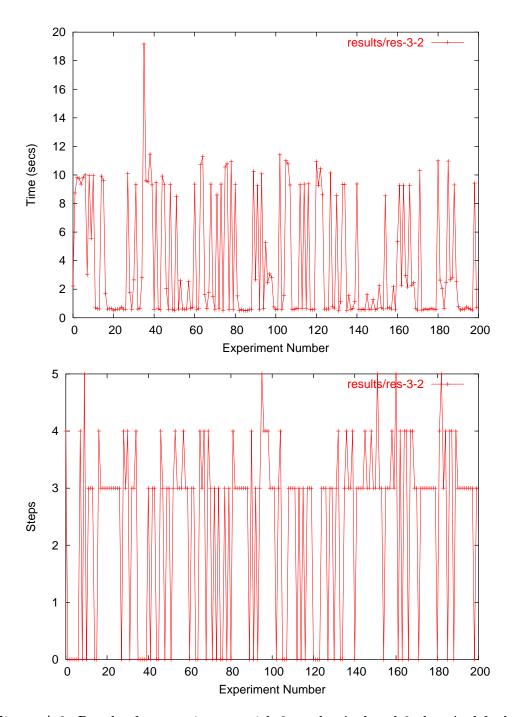

| A.1  | Results for experiments with 3 mech. and 0 elect. faults: cases 1-100.    | 222 |

| A.2  | Results for experiments with 3 mech. and 0 elect. faults: cases 101-200.  | 223 |

| A.3  | Results for experiments with 3 mech. and 2 elect. faults: cases 1-100.    | 224 |

| A.4  | Results for experiments with 3 mech. and 2 elect. faults: cases 101-200.  | 225 |

| A.5  | Results for experiments with 5 mech. and 0 elect. faults: cases 1-100.    | 226 |

| A.6  | Results for experiments with 5 mech. and 0 elect. faults: cases 101-200.  | 227 |

| A.7  | Results for experiments with 5 mech. and 3 elect. faults: cases 1-100.    | 228 |

| A.8  | Results for experiments with 5 mech. and 3 elect. faults: cases 101-200.  | 229 |

| A.9  | Results for experiments with 8 mech. and 0 elect. faults: cases 1-100.    | 230 |

| A.10 | Results for experiments with 8 mech. and 0 elect. faults: cases 101-200.  | 231 |

| A.11 | Results for experiments with 8 mech. and 5 elect. faults: cases 1-100.    | 232 |

| A.12 | Results for experiments with 8 mech. and 5 elect. faults: cases 101-200.  | 233 |

| A.13 | Results for experiments with 10 mech. and 0 elect. faults: cases 1-100.   | 234 |

| A.14 | Results for experiments with 10 mech. and 0 elect. faults: cases 101-200. | 235 |

| A.15 | Results for experiments with 10 mech. and 3 elect. faults: cases 1-100.   | 236 |

A.16 Results for experiments with 10 mech. and 3 elect. faults: cases 101-200.237 A.17 Results for experiments with 10 mech. and 5 elect. faults: cases 1-100. 238 A.18 Results for experiments with 10 mech. and 5 elect. faults: cases 101-200.239 A.19 Results for experiments with 10 mech. and 7 elect. faults: cases 1-100. 240 A.20 Results for experiments with 10 mech. and 7 elect. faults: cases 101-200.241

# List of Figures

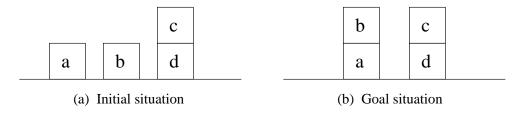

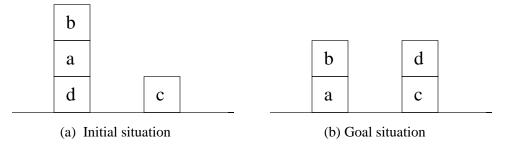

| 1.1 | Blocks World Domain                                                       | 8   |

|-----|---------------------------------------------------------------------------|-----|

| 1.2 | Blocks World Domain                                                       | 15  |

| 1.3 | Program describing the blocks world domain given as input to SMOD-        |     |

|     | ELS                                                                       | 18  |

| 1.4 | Results for blocks world program of Figure 1.3                            | 20  |

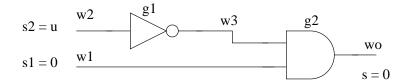

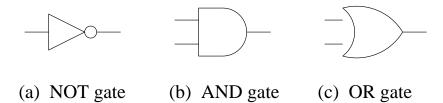

| 3.1 | Digital circuit with undefined input and defined output                   | 40  |

| 3.2 | Symbolic representation of basic gates                                    | 41  |

| 3.3 | Graphical representation of a digital circuit                             | 43  |

| 3.4 | Program to compute maximum delay of a circuit                             | 52  |

| 3.5 | (a) Output in numerical form. (b) Timing Analysis                         | 55  |

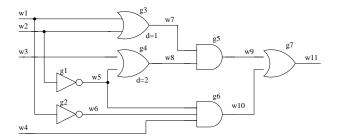

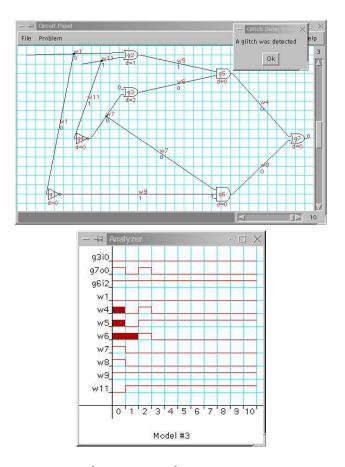

| 3.6 | Circuit with a hazard.                                                    | 56  |

| 3.7 | (a) ToolBox Window. (b) The complete circuit                              | 61  |

| 3.8 | Interface output for glitch detection problem                             | 63  |

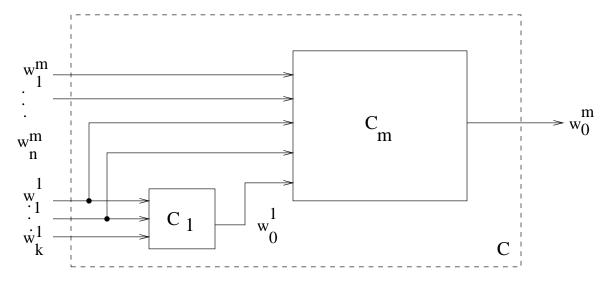

| 4.1 | Blocks diagram for digital circuit $C$ decomposed into circuits $C_m$ and |     |

|     | $C_1$                                                                     | 115 |

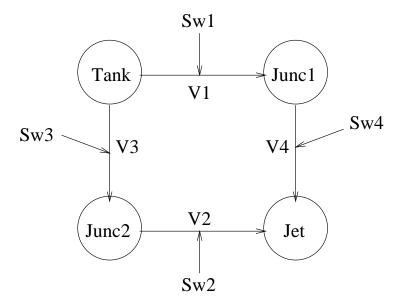

| 5.1 | A simplified view of the RCS                                              | 131 |

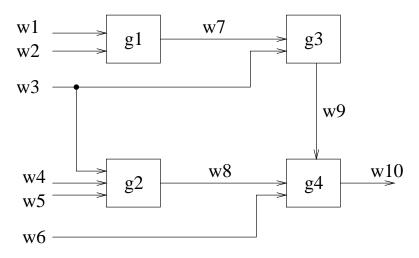

| 5.2 | A simplified view of a circuit                                            | 161 |

| 5.3 | A graphical representation of a faulty input wire                         | 169 |

| 5.4  | Initial situation common to all test instances of RCS planner            | 191 |

|------|--------------------------------------------------------------------------|-----|

| 5.5  | Test instance for RCS planner with 3 mechanical and 2 electrical faults. | 192 |

| 5.6  | Solution for test instance shown in Figure 5.5                           | 193 |

| 5.7  | Plan file corresponding to test instance shown in Figure 5.5             | 194 |

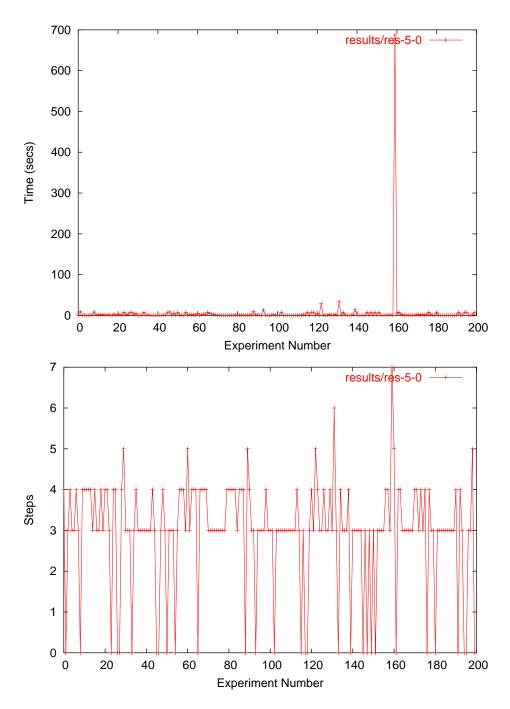

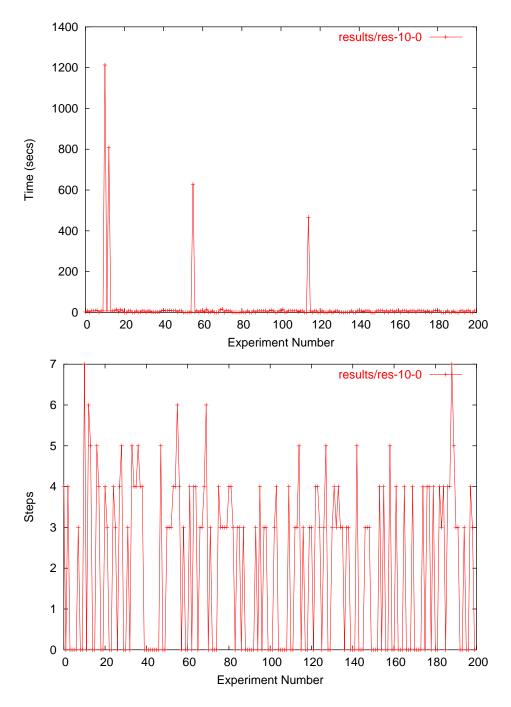

| A.1  | Results for experiments with 3 mechanical and 0 electrical faults. $$ .  | 212 |

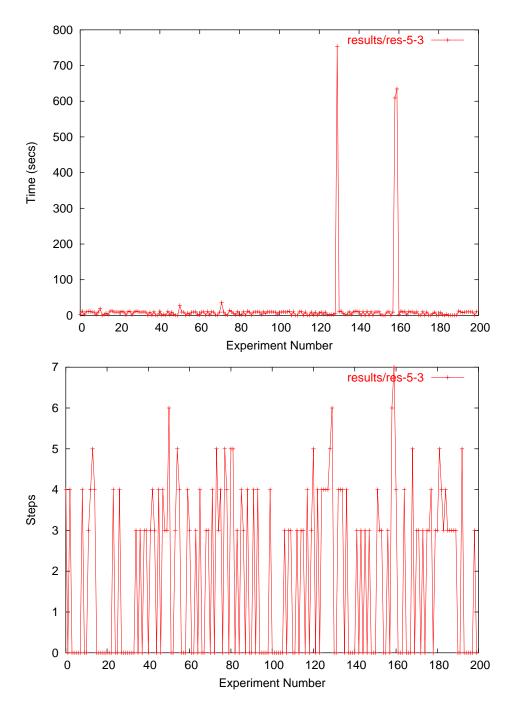

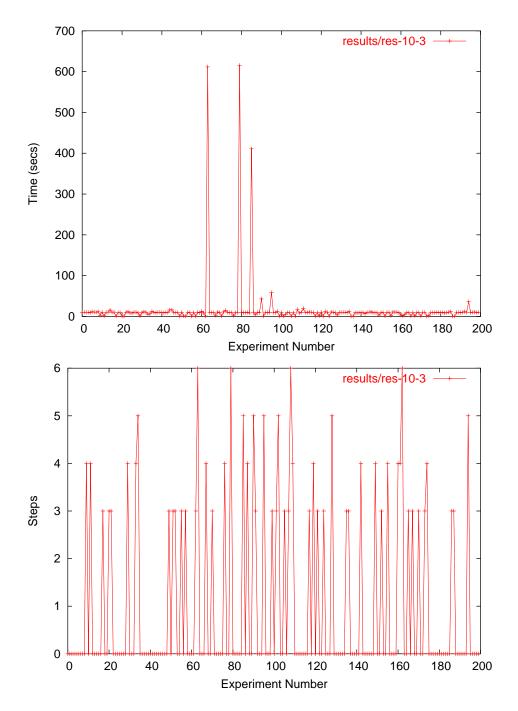

| A.2  | Results for experiments with 3 mechanical and 2 electrical faults. $$ .  | 213 |

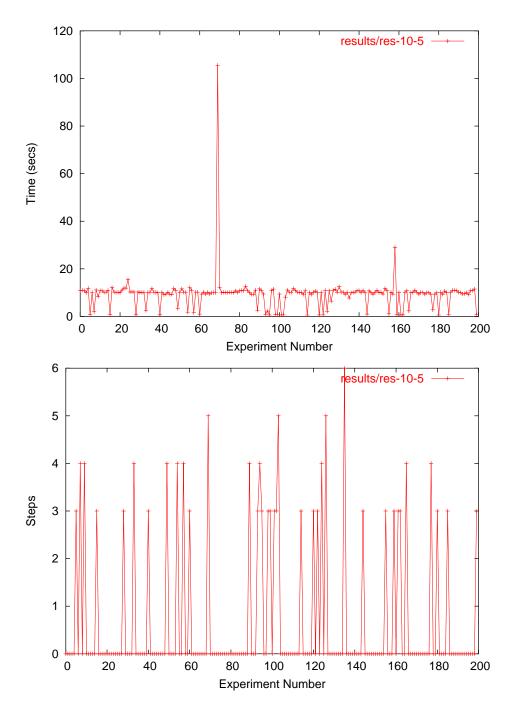

| A.3  | Results for experiments with 5 mechanical and 0 electrical faults. $$ .  | 214 |

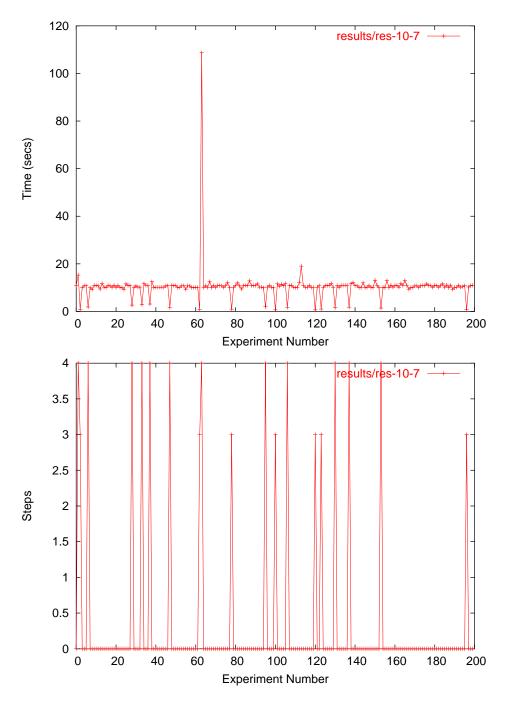

| A.4  | Results for experiments with 5 mechanical and 3 electrical faults. $$ .  | 215 |

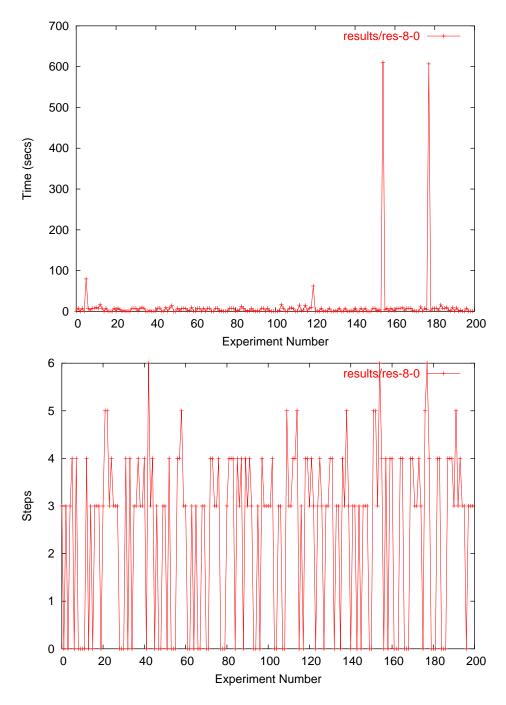

| A.5  | Results for experiments with 8 mechanical and 0 electrical faults. $$ .  | 216 |

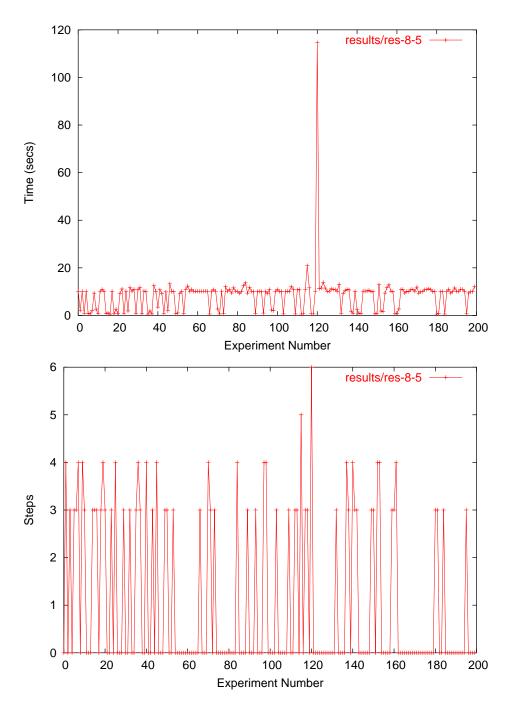

| A.6  | Results for experiments with 8 mechanical and 5 electrical faults. $$ .  | 217 |

| A.7  | Results for experiments with 10 mechanical and 0 electrical faults       | 218 |

| A.8  | Results for experiments with 10 mechanical and 3 electrical faults       | 219 |

| A.9  | Results for experiments with 10 mechanical and 5 electrical faults       | 220 |

| A.10 | Results for experiments with 10 mechanical and 7 electrical faults       | 221 |

## Chapter 1

### Introduction

"If I hear, I forget.

If I see, I remember.

If I do, I understand."

Proverb

In this chapter we present the background information necessary to understand the subject of this dissertation. The chapter is organized as follows. First, we discuss the avenues of research which originated from the idea of using logic to represent Artificial Intelligence (AI) related knowledge. Secondly, we cover the first difficulties encountered by the logic programming approach and the first nonmonotonic formalisms which sought to solve these problems. Next, we illustrate our programming methology through an example, using the famous blocks world domain. We present the goals and contributions of this work, and finally, we give the organization of the dissertation.

### 1.1 Logic Approach to AI

In 1959 [134], John McCarthy proposed the use of *logical formulas* to represent AI-related knowledge. He expressed the advantages of his idea as follows:

"Expressing information in declarative sentences is far more modular than expressing it in segments of computer programs or in tables. Sentences can be true in a much wider context than specific programs can be used. The supplier of a fact does not have to understand much about how the receiver functions, or how or whether the receiver will use it. The same fact can be used for many purposes because the logical consequences of collections of facts can be available."

The original approach was to use classical logic to represent and reason about various types of knowledge. Unfortunately, it was soon discovered that this approach may not be adequate for representing commonsense knowledge. In [148], Minsky discussed one such domain which involved describing birds' flying abilities.

This classical problem consisted of representing the statement

This is a typical example of a default - a statement "normally, typically, as a rule, elements of class C have property P." Reasoning with defaults and their exceptions seems to be essential in our everyday life. However, it does not occur in mathematics. Minsky argued that defaults cannot, in principle, be represented by the means of

logic. Indeed, suppose that the common knowledge about flying abilities of birds, including the following four statements:

- 1. Birds fly.

- 2. Penguins are birds.

- 3. Penguins do not fly.

- 4. Tweety is a bird.

is encoded by a theory  $\mathcal{T}$  of classical logic.

Clearly,  $\mathcal{T}$  should entail that "Tweety flies" since Tweety is a bird and birds fly. Now, if we happen to know that "Tweety is a penguin," adding this new knowledge to  $\mathcal{T}$  will make  $\mathcal{T}$  inconsistent. Theory  $\mathcal{T}$  will now entail that: (a) "Tweety flies," as before, and (b) "Tweety does not fly" because Tweety is a penguin and penguins do not fly.

Intuitively, we should be able to withdraw the previous conclusion, (a), and conclude (b) in the presence of the new knowledge. This example shows that classical logic is not suitable for formalizing commonsense knowledge.

Reasoning which permits retraction of previous conclusions when confronted with contradicting knowledge is called *nonmonotonic*. In more precise terms an entailment relation  $\models$  (over language  $\mathcal{L}$ ) is called *nonmonotonic* if there are formulas A and B and a set of formulas T such that  $T \models B$  and T,  $A \not\models B$ . Otherwise, the entailment is

said to be *monotonic*. Classical logic is monotonic. For formalization of commonsense we seem to need nonmonotonicity.

This realization led to the introduction of several formalisms which extend classical logic to allow for nonmonotonic reasoning. Some of the most important ones are Default Logic [169], Autoepistemic Logic [149, 150], and Circumscription [135, 136]. Meanwhile, another line of research led by Kowalski [107, 108] and Colmerauer [44], which originated with the introduction of the resolution principle by Robinson [173], and was influenced by Hayes' [94] idea that "computation is controlled deduction," concentrated on developing efficient algorithms that would allow for "programming in logic." This work gave birth to the first interpreter for the PROLOG Programming Language [45].

The language is based on definite Horn clauses. A definite clause has the form:

$$h \leftarrow a_1 \wedge \ldots \wedge a_n$$

where head h is either an atom, and body  $a_1 \wedge \ldots \wedge a_n$  is a conjunction of atoms. If the body is empty, the rule is called a fact. The symbol " $\leftarrow$ " is read as if. A program in PROLOG consists of a set of definite clauses, which can be interpreted both declaratively and procedurally. The semantics of a definite clause

$$p \leftarrow q \wedge r$$

can be perceived in one of the two following ways:

(a) p is true if q and r is true;

#### (b) to prove p, prove q and prove r.

The procedural interpretation is the basis for the implementation of the PROLOG language which answers queries about an input program P. If a query q has no variables, the interpreter returns "yes" if it finds a proof of q from P. Otherwise, it returns "no." If there are variables in the query, e.g. q(X), the system answers "no" if no terms satisfying the query are found, or returns the first "substitution" X = t that is found. The inference is based on the adaptation of Robinson's resolution [173] by [90, 91, 108].

A PROLOG program is often understood as a collection of clauses together with an interpreter. Even though programs

$$\Pi_0 \left\{ \begin{array}{ll} p \leftarrow p \\ p \end{array} \right. \quad \Pi_1 \left\{ p \right.$$

are equivalent declaratively, when viewed procedurally they exhibit different behaviors. Program  $\Pi_1$  stops and returns "yes" to query p, but program  $\Pi_0$  goes into an infinite loop when trying to find a proof for p.

Later, "Pure Prolog" of definite clauses was expanded by a new logical connective, not, called "negation as failure." The first interpretation of this connective was purely procedural and given in terms of the Prolog interpreter. A rule

$$p := q, not r$$

reads as "if q is proven and no proof for r is found, then p is proven." The symbol ":-" is read as if. A program consisting of this rule and the atom q answers "yes"

to p. Addition of r forces the program to withdraw its answer. The Prolog inference process becomes nonmonotonic. The problem of finding a declarative semantics for not proved difficult. The first pioneering work to give a semantics for not was done by: Clark [42] who introduced the negation as finite failure rule and the notion of completion of a logic program; Reiter [168] through the encoding of the Closed World Assumption; Apt, Blair, and Walker [5] who formalized the notion of stratification of logic programs; van Gelder, Ross, and Schlipf's [197] introduction of the well-founded semantics; and Gelfond and Lifschitz's [74] stable models/answer sets semantics. There are many other approaches. A survey of the use of negation in logic programming is presented in [6].

These two lines of research converged to develop the field of Logic Programming and Nonmonotonic Reasoning, and the A-Prolog language which extends "classical" Prolog by classical negation and disjunction. This language was shown to be closely connected with Default [78] and Autoepistemic Logic [129].

A-Prolog is a declarative logic programming language based on stable models/answer sets semantics [74, 75] of logic programs. It allows the encoding of defaults and various other types of knowledge contained in dynamic domains, e.g. the representation of actions and their effects. In recent years, the development of several different reasoning systems for A-Prolog led to the emergence of answer set programming [131, 152], a new programming paradigm. Currently, the most efficient inference

7

engines for A-Prolog are  $SMODELS^1$  [153, 154, 155, 156], and  $DLV^2$  [41, 55, 53, 54].

Another difficulty in the realization of McCarthy's program was discovered when researchers attempted to represent information about effects of actions.

To illustrate the issues involved in this type of reasoning we will use a classic AI example: the blocks world domain. It consists of a number of blocks which can sit directly on a table or be stacked up by action move block X on top of block Y. A similar action can be used to unstack a block and move it to the table or on top of another block.

To model this domain we need to represent blocks, which can easily be done with a collection of facts, e.g.

block(a).

block(b).

block(c).

block(d).

and the table denoted by t.

There are two types of locations where a block can sit: the top of another block or the table. The following two rules express that a location is either a block or the table.

location(X) :- block(X).

<sup>&</sup>lt;sup>1</sup>The smodels homepage is located at http://www.tcs.hut.fi/Software/smodels/

$<sup>^2{\</sup>rm The~DLV}$  home page is located at http://www.dbai.tuwien.ac.at/proj/dlv/

location(t).

A state of the domain is defined by the relation on(B,L), which says that block B is at location L. The truth value of this relation changes with time through the execution of action move(B,L), defined by rule

For instance, execution of action move(b, a) changes the state in Figure 1.1(a) into the state shown in Figure 1.1(b).

Figure 1.1: Blocks World Domain.

We would like to specify a transition diagram describing all the possible trajectories of the domain. To do that we need to define the state of the domain and the transition relation  $\langle \sigma_0, a, \sigma_1 \rangle$ , where  $\sigma_1$  is the state of the domain after action a is performed in previous state  $\sigma_0$ .

We start with introducing a relation holds(F,T) which defines that fluent F holds, i.e. is true, at time T. By T we mean a discrete time point. (For simplicity, we assume that the execution of each action takes one time unit.)

A state  $\sigma_0$  will be given by a collection of atoms holds(on(B,L),0); state  $\sigma_1$  - by a collection of atoms holds(on(B,L),1); a state k in the path  $\langle \sigma_0, a_0, \ldots, \sigma_k, a_k, \sigma_{k+1} \rangle$  will be given by a collection of atoms holds(on(B,L),k).

Explicit negative information is expressed in A-Prolog through the "classical negation" connective, denoted by  $\neg$ . Rule

provides negative information about positions of blocks. It says that a block B is not at a location  $L_2$  at time T if it is at a different location  $L_1$  at this time.

This rule is a logic programming variant of the so called "state constraint" (or static causal law) [132]

$$g if f (1.3)$$

which says that property g must be true in any state where property f is true. In this case,  $\neg on(B, L_2)$  if  $on(B, L_1), L_1 \neq L_2$ .

We also need to define the direct effects of actions. For that we write a "dynamic

causal law" of the form

$$a$$

causes  $f$  if  $p$   $(1.4)$

which says that performing action a causes property f to become true if preconditions p are true in this state.

In the blocks world domain this corresponds to rule

Relation occurs(move(B,L),T) defines an "observation" of the occurrence of action move(B,L) in the state T of the domain.

It is not always possible to execute such an action, e.g. if there exists a block  $B_1$  on top of block B then B cannot be moved. Knowledge of this type is referred to as an "impossibility condition," and is represented by rules with empty heads. The empty head of such a rule means that the body must be false in all models of the program. If the head is empty the rule is often called a "constraint."

The impossibility condition identified above is described by rule

```

:- block(B),

block(B1),

B ≠ B1,

```

```

location(L),

time(T),

occurs(move(B,L),T),

holds(on(B1,B),T).

(1.6)

```

It is also not possible to move a block B to a location L if there exists another block  $B_1$  at L, i.e.

```

:- block(B),

block(B1),

B ≠ B1,

location(L),

time(T),

occurs(move(B,L),T),

holds(on(B1,L),T).

(1.7)

```

The following constraint states that a block B cannot be moved on top of itself.

```

:- block(B),

time(T),

occurs(move(B,B),T).

(1.8)

```

Rules (1.2), (1.5), (1.6), (1.7), and (1.8) above describe the changes caused in the state of the domain by execution of action move(B,L). It is also necessary to describe what has not changed in the state of the domain after executing action a, i.e. which

fluents values have not been altered by a. In logic programming this can be done by the following default

```

\label{eq:holds} \begin{aligned} &\text{holds}(\text{on}(\texttt{B},\texttt{L}),\texttt{T+1}) :=\\ && &\text{block}(\texttt{B}),\\ && &\text{location}(\texttt{L}),\\ && &\text{time}(\texttt{T}),\\ && &\text{holds}(\text{on}(\texttt{B},\texttt{L}),\texttt{T}),\\ && && &\text{not} \ \neg \text{holds}(\text{on}(\texttt{B},\texttt{L}),\texttt{T+1}). \end{aligned} \tag{1.9}

```

which says that if a block B is at location L at time T, and there is no reason to believe it is not at L in the next moment of time T+1, then it is still there at T+1.

The above default encodes the *commonsense law of inertia* - "normally, things tend to stay as they are." Formalization of this default was proposed by McCarthy [137] as a possible solution for the *frame problem*. This famous problem, first pointed out in [138], consisted of describing concisely what should not change in the current state of the domain after an action is executed.

Negation as failure, which permits an elegant representation of defaults in A-Prolog, allows for a simple solution of this problem given by rule (1.9). The rule also helps solving the ramification and qualification problems. The ramification problem [66] consists of representing the indirect effects of actions. In A-Prolog it is solved by combining the inertia axiom with dynamic causal laws and state constraints. In the case of the blocks world - by rules (1.2), (1.5), and (1.9). If a block B is moved

from the table on top of another block  $B_1$ , then an indirect effect of the execution of this action will be that B is no longer on the table. The qualification problem [135] consists of describing in a concise way the (impossibility) conditions that would prevent the execution of an action. In A-Prolog this is done by writing constraints like (1.6), (1.7), and (1.8).

The resulting state  $\sigma_1$ , after the execution of an action a in a state  $\sigma_0$ , is often called a successor state [171]. It was difficult to define the values of fluents for successor states. The solution to the frame, ramification, and qualification problems made this possible. In A-Prolog these solutions are based on the concept of a transition diagram of the domain. There are various definitions of this diagram and its transition relation, [133, 194]. These definitions are independent of the notion of answer sets and based on various theories of causalities. A different definition of transition relation will be given below. (For details see [26]).

We first need to introduce the following notation.

Let  $\Pi_0$  be a program consisting of dynamic and static causal laws, the inertia axiom, and impossibility constraints, where time  $T \in \{0, 1\}$ . Let

$$holds(\sigma, k) = \{holds(f, k) : f \in \sigma\} \cup \{\neg holds(f, k) : \neg f \in \sigma\},\$$

and let occurs(a, 0) be an observation of the occurrence of action a at T = 0.

**Definition 1.1.** A transition  $\langle \sigma_0, a, \sigma_1 \rangle$  belongs to the transition diagram of the domain described by  $\Pi_0$  if there exists an answer set S of program

$$\Pi_0 \cup holds(\sigma_0, 0) \cup \{occurs(a, 0)\}$$

such that

(a)

$$f \in \sigma_1$$

iff  $holds(f, 1) \in S$ ;

(b)

$$\neg f \in \sigma_1 \text{ iff } \neg holds(f, 1) \in S.$$

There is a remarkable relationship between the logic programming based definition of the transition diagram given above and the causality based definitions from [133, 194]. This relationship not only establishes the close connection between causality and beliefs but also allows us to reduce various reasoning tasks of a dynamic agent to computing answer sets of various programs. For instance, program  $\Pi_0$  can be used to solve classical AI tasks like planning and diagnosis. Let us illustrate the basic idea of this reduction by an example:

Consider the initial situation  $\sigma_0$  for the blocks world domain, shown in Figure 1.2(a), and goal situation  $\sigma_n$ , shown in Figure 1.2(b).

The initial situation  $holds(\sigma_0, 0)$  is described by facts

holds(on(a,d),0).

holds(on(b,a),0).

holds(on(c,t),0).

Figure 1.2: Blocks World Domain.

```

holds(on(d,t),0).

```

The goal  $\mathcal{G}(\sigma_n, T)$  is represented by rules

which describe what must be true in the goal situation, and the constraint below that

eliminates all models not satisfying the goal.

To find a plan of length not exceeding n, i.e. T < n, let us take program  $\Pi_n$ , which is program  $\Pi_0$  with time now ranging from 0 to n, and expand this program in the following way. The generation phase of planning will be implemented using a *choice* rule CR, which has the form

$$1\{occurs(A,T):action(A)\}1:-$$

$$time(T),$$

$$T < n,$$

$$not goal(T).$$

This rule states that, for each time point T < n, if the goal has not been reached, then an action must occur at that time.

Choice rules are part of the language of SMODELS [155]. The head of the choice rule has the form

$$L\{p(\bar{X}):q(\bar{X})\}U.$$

It defines a subset  $p \subseteq q$  of terms such that  $L \leq |p| \leq U$ . Normally, there are many possible sets satisfying these conditions. Hence, a program containing this type of rules might have multiple answer sets, corresponding to possible choices of p. Choice rules do not extend the expressive power of the logic programming language and can be viewed as a shorthand for a set of standard rules of the language. These rules,

however, proved to be very convenient. They substantially shorten the program, and more importantly, they allow for an efficient implementation.

The problem of finding a plan to move from  $\sigma_0$  to  $\sigma_n$ , of length not exceding n, can be reduced to finding an answer set of program

$$\Pi_n \cup holds(\sigma_0, 0) \cup \mathcal{G}(\sigma_n, T) \cup \mathcal{C}R.$$

It is easy to check, using SMODELS, that we can find an answer set of this program corresponding to a plan which achieves this goal. One such plan is

$$\langle occurs(move(b,t),0), occurs(move(a,t),1), \\ occurs(move(b,a),2), occurs(move(d,c),3) \rangle$$

There are other plans and other answer sets. The complete program given as input to SMODELS is shown in Figure 1.3. Notice that the rules in the program are slightly different from the ones we presented here, in order to accommodate SMODELS syntax and type requirements. We also use SMODELS' display formatting capabilities, e.g.  $hide\ p(X)$ , in order to display just the atoms that constitute a plan. All plans, of length not exceeding 4 steps, which achieve the goal described in this example are given in Figure 1.4, and were computed in 0.06 seconds. There exists no answer set corresponding to a plan of length smaller than 4.

The answer set programming paradigm was shown to be adequate for comparatively small problems/domains. Although most of the attention was given to answer set planning [48, 120], diverse interesting problems have been so far solved using answer

```

% Objects of the domain

block(a).

block(b).

block(c).

block(d).

location(X) :- block(X).

location(t).

action(move(B,L)).

% State constraint (Static Causal Law)

-holds(on(B,L1),T) := holds(on(B,L),T), neq(L,L1).

% Dynamic Causal Law

holds(on(B,L),T+1) := occurs(move(B,L),T).

% Inertia Law

holds(on(B,L),T+1) := holds(on(B,L),T), not -holds(on(B,L),T+1).

% Impossibility conditions

% Constraint 1:

% A block topped by another block cannot be moved.

:- occurs(move(B,L),T), holds(on(B1,B),T), neq(B,B1).

% Constraint 2:

% A block cannot be moved to a location occupied by another block.

:- occurs(move(B,L),T), holds(on(B1,L),T), neq(B,B1), neq(L,t).

% Constraint 3:

% A block cannot be moved on the top of itself.

:- occurs(move(B,B),T).

% Plan generation rule

1\{occurs(A,T):action(A)\}1 :- T < lasttime, not goal(T).

```

Figure 1.3: Program describing the blocks world domain given as input to SMODELS.

```

Blocks World Program (cont.)

% Initial situation

holds(on(a,d),0).

holds(on(b,a),0).

holds(on(c,t),0).

holds(on(d,t),0).

% Goal situation

goal(T) :- holds(on(a,t),T),

holds(on(b,a),T),

holds(on(c,t),T),

holds(on(d,c),T).

goal :- goal(T).

:- not goal.

% Time definition

% Maximum plan length is determined by constant lasttime, provided by

% user at run time.

time(0..lasttime).

% Types definition

#domain time(T).

#domain block(B;B1).

#domain location(L;L1).

% Display formatting commands

hide block(X).

hide location(X).

hide action(X).

hide holds(X,Y).

hide time(X).

hide goal.

```

Figure 1.3: Program describing the blocks world domain given as input to SMODELS.

```

Results for Blocks World Program

% Command line for SMODELS to compute all answer sets of blocks_world

% input program

lparse --true-negation -c lasttime=4 blocks_world | smodels 0

% Result of computation

smodels version 2.26. Reading...done

Answer: 1

Stable Model: occurs(move(b,t),0) occurs(move(a,t),1)

occurs(move(d,c),2) occurs(move(b,a),3)

Answer: 2

Stable Model: occurs(move(b,t),0) occurs(move(a,t),1)

occurs(move(b,a),2) occurs(move(d,c),3)

Answer: 3

Stable Model: occurs(move(b,c),0) occurs(move(a,t),1)

occurs(move(b,a),2) occurs(move(d,c),3)

False

Duration: 0.060

Number of choice points:

Number of wrong choices:

Number of atoms: 384

Number of rules:

1344

Number of picked atoms:

Number of forced atoms:

Number of truth assignments:

```

Figure 1.4: Results for blocks world program of Figure 1.3.

Size of searchspace (removed): 8 (6)

set programming, e.g. product configuration [184], wire routing [61], etc. In this dissertation, we developed a substantially larger application.

#### 1.2 Goals and Contributions of this work

The goals of this work are to answer the following two questions:

- 1. Is it possible to represent a real world problem of reasonable size involving complex effects of actions with the A-Prolog language?

- 2. Are the available inference engines for A-Prolog able to compute the solutions to such a domain in a reasonably efficient manner?

We address these questions in two steps.

The first step was inspired by my work aimed at representing knowledge about digital circuits for the Digital Design II graduate class at The University of Texas at El Paso. In this class, students were required to learn a Hardware Description Language (HDL) [30, 84], VHDL [101, 176] or Verilog HDL [159, 160, 186], in order to complete a class project. This project consisted of representing and simulating a digital circuit using the language and its simulator. The size and complexity of these languages soon led me to wonder if it would not be possible, and simpler, to complete these tasks using a declarative language, more specifically, the A-Prolog language. Because it provides an extensive range of capabilities, the VHDL language is considered complex and difficult to understand, even by experienced digital designers [84]. Verilog's syntax is

similar to the C programming language, and is regarded by designers as an easy to learn and teach language because of its compact size [160]. This is an understimation caused by the ever present comparison between Verilog and VHDL, the two most popular Hardware Description Languages today. My limited experience with Hardware Description Languages increased my difficulties and motivated me to program the assignment in A-Prolog. At that point, the original question now focused on whether A-Prolog would allow the representation of digital circuits in a simpler way and if the language would be powerful enough to also permit the simulation of such circuits. Results were positive and satisfactory in both accounts. We designed a simple tool the A-Circuit<sup>3</sup> system [14], that can be used by students in Digital Design or other related classes, to represent and simulate (simple) digital circuits. One main advantage of our approach is the use of a single language to describe both structure and behavior of gates, and as a simulation environment, which results in a uniform approach to the simulation of digital circuits. The A-Circuit system also incorporates some other more sophisticated tasks, which cannot currently be achieved by using traditional HDL languages. In some cases, several HDL related tools must be used in order to achieve a task; in other cases, e.g. diagnosis, HDL languages still cannot support such features. We discuss the design of the A-Circuit system in Chapter 3. The correctness of the system is proved by various propositions. Chapter 4 presents

<sup>3</sup>The A-Circuit system is available for download from: http://www.krlab.cs.ttu.edu/Download/A-Circuit/

these proofs.

The second step was more ambitious. We got involved in a real world application, a project supported by NASA's major contractor, the United Space Alliance (USA) company. The objectives of the project were:

- 1. to represent information about some subsystems of the space shuttle; and

- 2. to design a decision support system for flight controllers of the shuttle.

The high expressive power and simplicity of the A-Prolog language were fundamental to the success of the project. Both objectives of the project were satisfactorily accomplished and the reception of our results, reported in the *Third International NASA Workshop on Planning and Scheduling for Space*, in September 2002 [18], was very positive.

The representation of the space shuttle's RCS system, which corresponds to the first objective above, is presented in Section 5.3 of Chapter 5; the design of the decision support system, USA- $Advisor^4$ , the second objective mentioned, is discussed in Section 5.4 of the same chapter. This application involved a substantial amount of knowledge representation, as well as the design and implementation of some tasks, such as plan checking and actual planning. These tasks are discussed in Sections 5.5 and 5.6 of Chapter 5.

<sup>&</sup>lt;sup>4</sup>The RCS/USA-Advisor system is available for download from: http://krlab.cs.ttu.edu/~marcy/RCS/

### 1.3 Organization of the dissertation

This dissertation is organized in the following way. The next chapter presents the syntax and semantics of the A-Prolog language. The description and discussion about the design of the A-Circuit system is given in Chapter 3. Theorems and related proofs are presented in Chapter 4. The representation of the space shuttle's RCS system and the design of the USA-Advisor decision support system are described in Chapter 5. Conclusions, lessons learned, related and future work are discussed in Chapter 6. Appendix A presents tables and graphs summarizing the results of the experiments with the RCS system.

## Chapter 2

## The A-Prolog Language

"A representation is called epistemologically adequate for a person or machine if it can be used pratically to express the facts that one actually has about the aspect of the world. A representation is called heuristically adequate if the reasoning processes actually gone through in solving a problem are expressible in the language."

John McCarthy and Patrick Hayes [138]

The A-Prolog language, [71, 73], is a declarative logic programming language based on stable models/answer sets semantics of logic programs [74, 75]. A-Prolog allows the representation of defaults and multiple interesting aspects of reasoning about actions and their effects. We start by defining the syntax and semantics of A-Prolog as given in [71, 73].

## 2.1 Syntax

The syntax of A-Prolog is determined by a signature  $\Sigma = \langle \mathbf{T}, \mathbf{C}, \mathbf{F}, \mathbf{P} \rangle$  where  $\mathbf{T}, \mathbf{C}, \mathbf{F},$  and  $\mathbf{P}$  are sets of symbols. Members of the set  $\mathbf{T}$  are called *types*. The

set C contains object constants for each type in T. Symbols from sets F and P are typed functions and predicate constants, respectively. Each function symbol and predicate symbol has an associated integer called its arity. It is assumed that the signature contains symbols for integers and for the standard functions and relations of arithmetic. A term of  $\Sigma$  is either a typed object constant, or a string of the form  $f(t_1,\ldots,t_n)$ , where  $t_1,\ldots,t_n$  are terms of the proper types, and f is a typed function symbol of arity n. An atom is a string of the form  $p(t_1, \ldots, t_n)$ , where p is a typed predicate symbol of arity n in  $\Sigma$ , and  $t_1, \ldots, t_n$  are terms of the corresponding types. A literal is either an atom (also called a positive literal), or an atom preceded by  $\neg$  (a negative literal). The symbol  $\neg$  is called *classical* or *strong* negation. Literal  $\neg a$  is read as "a is believed to be false," under the (epistemic) interpretation of logic programs of [75]. For a literal l, by  $\overline{\neg l}$  we mean l, and by  $\overline{l}$  we mean  $\neg l$ . Literals l and  $\neg l$  are called contrary. Literals and terms not containing variables are called ground. The sets of all ground terms, atoms and literals over  $\Sigma$  are denoted by  $terms(\Sigma)$ ,  $atoms(\Sigma)$ , and  $lit(\Sigma)$ , respectively. For a set P of predicate symbols from  $\Sigma$ ,  $atoms(P,\Sigma)(lit(P,\Sigma))$ denote the sets of ground atoms (literals) of  $\Sigma$  formed with predicate symbols from P. A set of literals is said to be *consistent* if it does not contain contrary literals. Consistent sets of ground literals over signature  $\Sigma$  containing all arithmetic literals which are true under the standard interpretation of their symbols are called *states* of  $\Sigma$  and denoted by  $states(\Sigma)$ .

A rule of A-Prolog is a statement of the form:

$$l_0 \leftarrow l_1, \dots, l_m, not \ l_{m+1}, \dots, not \ l_n \tag{2.1}$$

where  $n \geq 1$ , and  $l_i$ 's are literals over  $\Sigma$ . Literal  $l_0$  is called the *head* of the rule, and  $l_1, \ldots, l_m, not \ l_{m+1}, \ldots, not \ l_n$  constitutes the *body* of the rule. The symbol *not* is a logical connective called *negation as failure* or *default negation*. An expression *not* l is read as "there is no reason to believe in l." The head  $l_0$  can be either a literal or the symbol  $\bot$ . If  $l_0 = \bot$ , rule (2.1) is called a *constraint*. We frequently omit the head,  $\bot$ , of a constraint rule.

We assume that literals  $l_i$  in rules (2.1) are ground. We use rules with variables as a shorthand for the sets of their ground instantiations. Variables are denoted by capital letters.

A logic program is a pair  $\{\Sigma, \Pi\}$  where  $\Sigma$  is a signature and  $\Pi$  is a collection of rules over  $\Sigma$ .

A literal  $l \in lit(\Sigma)$  is true in a state S of  $\Sigma$  if  $l \in S$ ; l is false in S if  $\overline{l} \in S$ . Otherwise, l is unknown. The symbol  $\bot$  is false for any S.

#### 2.2 Semantics

A program  $\Pi$  in A-Prolog can be viewed as a specification given to a rational agent for constructing beliefs about possible states of the world. Technically, these beliefs are captured by the notion of an answer set of program  $\Pi$ . First, we give the precise definition of answer sets for programs whose rules do not contain negation as failure. Let  $\Pi$  be such a program and let S be a state of  $\{\Sigma, \Pi\}$ . Set S is said to be *closed* under  $\Pi$  if, for every rule  $head \leftarrow body$  of  $\Pi$ , head is true in S whenever body is true in S. A constraint rule is closed under  $\Pi$  if its body is not contained in S.

#### Definition 2.1. (Answer set of programs without default negation)

An answer set of a program  $\Pi$ , consisting of rules not containing default negation, is the smallest set S of ground literals of  $\Sigma$  which satisfies the following two conditions:

- 1. S is closed under the rules of  $ground(\Pi)$ , i.e., for every rule (2.1) in  $\Pi$ , either there is a literal l in its body such that  $l \notin S$  or its non-empty head  $l_0 \in S$ .

- 2. If S contains an atom p and its negation  $\neg p$ , then S contains all ground literals of the language.

It is not difficult to show that there is at most one set  $(Cn(\Pi))$  satisfying these conditions.

Now, let  $\Pi$  be an arbitrary ground program in A-Prolog. For any set S of ground literals of its signature  $\Sigma$ , let the reduct of  $\Pi$  relative to S, denoted  $\Pi^S$ , be the program obtained from  $\Pi$  by deleting:

- (i) each rule that has an occurrence of not l in its body with  $l \in S$ ,

- (ii) all occurrences of not l in the bodies of the remaining rules.

#### Definition 2.2. (Answer set of arbitrary programs)

Set S is an answer set of  $\Pi$  if

$$S = Cn(\Pi^S). \tag{2.2}$$

We are interested only in *consistent* programs, i.e., programs with at least one consistent answer set. Let S be an answer set of  $\Pi$ . A ground literal l is true in S if  $l \in S$ ; false in S if  $\neg l \in S$ . This is expanded to conjunctions and disjunctions of literals in a standard way.

#### Definition 2.3. (Entailment)

A program  $\Pi$  entails a literal l ( $\Pi \models l$ ) if l is true in all answer sets of  $\Pi$ . Program  $\Pi$  answers yes to a query l if  $\Pi \models l$ ; no if  $\Pi \models \overline{l}$ , and unknown otherwise.

Here are some examples. Assume that the signature  $\Sigma$  contains two object constants a and b. The program

$$\Pi_1 \begin{cases} q(a). \\ \neg p(X) \leftarrow not \ q(X). \end{cases}$$

has the unique answer set  $S = \{q(a), \neg p(b)\}$ . The program

$$\Pi_2 \left\{ \begin{array}{l} p(a) \leftarrow not \ p(b). \\ p(b) \leftarrow not \ p(a). \end{array} \right.$$

has two answer sets,  $\{p(a)\}\$  and  $\{p(b)\}\$ . The programs

$$\Pi_3 \ \Big\{ \ p(a) \leftarrow not \ p(a).$$

and

$$\Pi_4 \left\{ \begin{array}{l} p(a). \\ \leftarrow p(a). \end{array} \right.$$

have no answer sets.

It is easy to see that programs of A-Prolog are nonmonotonic. For example consider program  $\Pi_1$ . We saw that  $\Pi_1 \models \neg p(b)$ , however, if some new information, q(b), is added to the program, it forces the withdrawal of the previous conclusion  $\neg p(b)$ . The new program  $\Pi_1 \cup \{q(b)\}$  has the unique answer set  $\{q(a), q(b)\}$ . Nonmonotonic reasoning is important for the representation of commonsense knowledge, and gives the means for reasoning about time and change. A-Prolog is closely connected with more general nonmonotonic theories. In particular, as was shown in [75, 129], there is a simple and natural mapping of programs in A-Prolog into a subclass of Reiter's default theories [169]. Similar results are also available for Autoepistemic Logic [150].

Next, we present some important theorems and lemmas that exhibit nice properties of A-Prolog programs. They will be frequently used in the proofs of Chapter 4.

First, we introduce some necessary notation.

Let r be a rule of the form (2.1). By head(r), pos(r), and neg(r) we denote  $\{l_0\}$  and the sets  $\{l_1, \ldots, l_m\}$ , and  $\{l_{m+1}, \ldots, l_n\}$ , respectively. lit(r) denotes the set  $head(r) \cup pos(r) \cup neg(r)$ . For a program  $\Pi$ ,  $lit(\Pi)$  denotes the set of literals occurring in  $\Pi$ . For a program  $\Pi$  over the A-Prolog language, a set of literals A, over the language, is a splitting set of  $\Pi$  if for every rule  $r \in \Pi$ ,  $head(r) \cap A \neq \emptyset$  implies  $lit(r) \subseteq A$ .

Let A be a splitting set of  $\Pi$ . The bottom of  $\Pi$  relative to A, denoted by  $b_A(\Pi)$ , is the program consisting of all rules  $r \in \Pi$  such that  $lit(r) \subseteq A$ .

Given a splitting set A for  $\Pi$ , and a set X of literals from  $lit(b_A(\Pi))$ , the partial evaluation of  $\Pi$  by X with respect to A, denoted by  $e_A(\Pi, X)$ , is the program obtained from  $\Pi$  as follows. For each rule  $r \in \Pi \setminus b_A(\Pi)$  such that

- 1.  $pos(r) \cap A \subseteq X$ ;

- 2.  $neg(r) \cap A$  is disjoint from X;

there is a rule r' in  $e_A(\Pi, X)$  such that

- 1. head(r') = head(r), and

- 2.  $pos(r') = pos(r) \setminus A$ ,

- 3.  $neg(r') = neg(r) \setminus A$ .

Let A be a splitting set of  $\Pi$ . A solution to  $\Pi$  with respect to A is a pair  $\langle X, Y \rangle$  of set of literals satisfying the following two properties:

- 1. X is an answer set of  $b_A(\Pi)$ ;

- 2. Y is an answer set of  $e_A(\Pi \setminus b_A(\Pi), X)$ ;

- 3.  $X \cup Y$  is consistent.

#### Theorem 1. (Splitting Set Theorem, [122])

Let A be a splitting set for a program  $\Pi$ . A set A of literals is a consistent answer set of  $\Pi$  iff  $A = X \cup Y$  for some solution  $\langle X, Y \rangle$  to  $\Pi$  with respect to A.

The following example illustrates the notion of a splitting set and the use of the Splitting Set Theorem for the computation of answer sets of logic programs.

Let  $\Pi_0$  be the program consisting of the following rules

$$\Pi_0 \left\{ egin{array}{l} r(b) \leftarrow q(a). \\ q(a) \leftarrow not \ p(a). \\ p(a) \leftarrow p(b). \\ p(b). \end{array}

ight.$$

Set  $A_0 = \{p(a), p(b)\}$  splits  $\Pi_0$  into bottom program,  $b_{A_0}(\Pi_0)$ , and top program,  $t_{A_0}(\Pi_0)$ . The last two rules of  $\Pi_0$  belong to the bottom, and the first two rules form the top. It is easy to see that the bottom program has the unique answer set  $X = \{p(a), p(b)\}$ . (Notice that  $A_0 = X$  in this example, but this is not always the case.) The partial evaluation of the top with respect to  $A_0$  and the answer set X of the bottom, denoted  $e_{A_0}(\Pi, X)$ , is obtained by dropping its second rule which is falsified by the negated subgoal p(a). The result of the simplification is the program consisting of a single rule

$$e_{A_0}(\Pi_0, X) \left\{ r(b) \leftarrow q(a). \right.$$

It is easy to see that the unique answer set of  $e_{A_0}(\Pi_0, X)$  is  $Y = \{\}$ . Therefore, the only answer set for  $\Pi_0$ , denoted by  $\mathcal{A}$ , can be obtained by adding the unique answer

set of the bottom, X, to Y, i.e.

$$\mathcal{A} = X \cup Y = \{p(a), p(b)\}.$$

#### Lemma 2.1. (Marek and Subrahmanian, [128])

For any answer set S of a logic program  $\Pi$  consisting of rules of the form (2.1)

- (a) for any instance r of a rule of the type (2.1) from  $\Pi$ , if  $pos(r) \subseteq S$  and  $neg(r) \cap S = \emptyset$  then  $head(r) \in S$ ;

- (b) if S is consistent and  $l_0 \in S$  then there exists an instance r of a rule of the type (2.1) from  $\Pi$ , such that  $pos(r) \subseteq S$ ,  $neg(r) \cap S = \emptyset$ , and  $head(r) = l_0$ .

The previous example is used again to illustrate the applicability of Lemma 2.1 for the computation of answer sets of logic programs.

Let us take program  $\Pi_0$ . First, Lemma 2.1 will be used to compute an answer set of  $\Pi_0$  as follows.

By condition (a) of Lemma 2.1 and the last rule of  $\Pi_0$ ,

$$p(b)$$

.

it trivially follows that

$$p(b)$$

must belong to all answer sets of  $\Pi_0$ . (2.3)

Since p(b) is a consequence of  $\Pi_0$ , given condition (a) of Lemma 2.1, and the third rule of  $\Pi_0$ ,

$$p(a) \leftarrow p(b)$$

.

we have that

$$p(a)$$

must belong to all answer sets of  $\Pi_0$ . (2.4)

Statement (2.4) falsifies the second rule of  $\Pi_0$

$$q(a) \leftarrow not \ p(a)$$

.

Because of this fact, and since there exists no other rule in  $\Pi_0$  with head q(a), it follows that

$$q(a)$$

does not belong to any answer set of  $\Pi_0$ . (2.5)

Hence, no answer set of  $\Pi_0$  can satisfy the first rule

$$r(b) \leftarrow q(a)$$

.

Given this fact, and since there exists no other rule in  $\Pi_0$  with head r(b), we can conclude that

$$r(b)$$

does not belong to any answer set of  $\Pi_0$ . (2.6)

The above argument can be viewed as a construction of a set  $\mathcal{A}$  which must be a subset of any answer set of  $\Pi_0$ . We will show that  $\mathcal{A}$  is indeed an answer set of  $\Pi_0$ . To do that, let us compute the reduct of  $\Pi_0$  with respect to  $\mathcal{A}$ ,  $\Pi_0^{\mathcal{A}}$ . It consists of the following rules

$$\Pi_0^{\mathcal{A}} \begin{cases} r(b) \leftarrow q(a). \\ p(a) \leftarrow p(b). \\ p(b). \end{cases}$$

It is easy to see that  $\mathcal{A}$  is an answer set of  $\Pi_0^{\mathcal{A}}$ . Hence, by the definition of answer sets  $\mathcal{A}$  is an answer set of  $\Pi_0$ .

## Chapter 3

# Digital Circuits in A-Prolog

"There are two ways of constructing a software design; one way is to make it so simple that there are obviously no deficiencies, and the other way is to make it so complicated that there are no obvious deficiencies. The first method is far more difficult."

Sir Charles Antony Richard Hoare

Digital circuits have been extensively studied. However, in most logical approaches, circuits are described by propositional formulas [143, 144]. In our work we use logic programming and build a general theory of digital circuits which contains standard knowledge about circuits from the electrical engineering field.

## 3.1 Digital Circuits in Electrical Engineering

We start by reviewing the meaning of some terms of the electrical engineering field that are used in this work.

An electronic *gate*, or component, is a device that realizes a logical function. Roughly, *circuit* is a collection of interconnected gates.

In the electrical engineering field, a *signal* is an impulse or a fluctuating electric quantity, such as voltage, or current, whose variations represent coded information. In the area of digital electronics, the precise values of voltage signals, either applied or generated by components and circuits, are not significant toward determination of the logical operation of the gates/circuits; in fact, these values vary from circuit to circuit and from component to component [105]. More importantly, electronic gates are limited by construction to recognize only two ranges of values, "high" and "low," which are, by convention, associated with constants 1 and 0, respectively.

Input (and conversily, output) has been used as a technical term for probably more than a century in the field of physics, then in electrical engineering, and more recently in computer science. In this thesis, input/output (of a component or a circuit) are applied to the domain of electrical engineering. Both terms have been largely misused, but normally each have one of two meanings when used in this domain. Input conveys:

(a) energy or power, i.e. a signal, used to activate or drive a component/circuit, or (b) wire or pin at which a (input) signal enters a gate/circuit. By output it is meant: (a) energy or power, i.e. a signal, produced by a component/circuit, or (b) wire or pin at which a (output) signal produced by a gate/circuit is present. Even more confusely, it is possible that the term is used to indicate both concepts (as in items (a) and (b) mentioned before), simultaneously.

For clarity purposes, whenever referring to input[output] as energy or power, we use the expressions "input[output] signal," or "input[output] value"; and for indicating a wire or pin, we use the term "input[output] wire."

A *circuit* is a collection of interconnected electric components, called *gates*, where the output signal present on the output wire of one component is used to actuate (stimulate) one or more input wires of other components.

A combinational circuit is a circuit whose output signals are functions of only the current circuit input signals.

The propagation delay of a gate g is the time required to propagate an input signal through g, or to switch the output of g from a value to another.

For simplicity of exposition we restrict this work to circuits that have a single output wire. This implies that the output wire of each and all gates in a circuit, with the exception of a single one, must be connected to at least one input wire of one, or more, gates in the circuit. Moreover, the time required to propagate the input signal values applied to the input wires of a circuit to its output wire will be referred to as the "propagation delay of the circuit."

### 3.2 Formalization of Digital Circuits

Normally, computer science students start to study foundations of digital design in their first or second year at the university. First, they concentrate on combinational circuits which are constructed from simple boolean gates and are used to compute boolean functions. Given such a function  $Y = f(X_1, \ldots, X_n)$ , where Y and

$X_1,\ldots,X_n$  are boolean variables, students learn how to use propositional logic to construct a circuit C which instantaneously transforms the values  $X_1, \ldots, X_n$  applied on its input wires  $W_1, \ldots, W_n$  to the value Y on its output wire  $W_o$ . Later, they move to building more complex devices employing more complex, sequential circuits. The model of a circuit remains, however, essentially boolean with the only possible signals corresponding to 0 and 1, and basic gates still performing instantaneous transmission of information. In more advanced classes students normally "discover" that the boolean model they have learned is not always a realistic one. Gates suffer from physical limitations, i.e., do not instantaneously perform the function that they implement because of propagation (and other types) of delays. For a short time, the values of signals may lie somewhere between the levels necessary to classify them as 0 and 1, and will therefore be undefined. There are other situations where the analog (continuous and non-digital) character of gates and signals should be taken into account. To model such phenomena, scientists introduced the notion of a digital circuit with delays ([146, 201]) and three possible input values: 0, 1, and 1/2 (undefined) [201]. These circuits do not instantaneously produce the values of the corresponding functions. Instead, these values are produced after delays, which are determined by the circuit and the vector of input signals.

This approach mimics reality and allows input signal values  $s = \{0, 1, u\}$ , where u stands for an undefined value. In this case, input signal values  $S_1, \ldots, S_n$ , where  $S_i \in s$ , applied to input wires  $W_1, \ldots, W_n$  of a circuit C, are converted by a function

$S = g(S_1, \ldots, S_n)$  to the output value S on the output wire  $W_o$  of C.

To make it usable for mathematical proofs, this explanation needs to be clarified.

**Definition 3.1.** Let  $s = \{0, 1, u\}$  be the set of possible signal values on wires of a circuit C. Let  $g: S^n \to S$  be the function computed by C when values  $S_1, \ldots, S_n$  are applied to input wires  $W_1, \ldots, W_n$  of C at time t. Let  $\delta$  be a non-negative integer. We say that circuit C computes  $g(S_1, \ldots, S_n)$  with a delay  $\delta$  if, in the absence of other inputs, the value on its output wire  $W_o$  at any time  $t' \geq t + \delta$  is equal to S. C computes function g with a delay  $\delta$  if it computes all the values of g with this delay.

Notice that there are cases where even if some input signal value is undefined the circuit's output signal is a defined value. Figure 3.1 shows an example of a circuit with an input signal value undefined but whose output value is 0. The circuit consists only of a NOT and an AND gate with no delays. We show the graphical representation of the three basic gates NOT, AND, and OR on Figure 3.2 and their behavior, in the presence of the "undefined" (u) value, is presented in Table 3.1.

It is important to point out that our use of a 3-valued logic does not affect the *principle* of duality [105] which characterizes operations AND and OR from Boolean algebra.

Figure 3.1: Digital circuit with undefined input and defined output.

Figure 3.2: Symbolic representation of basic gates.

| NOT gate |        |  |

|----------|--------|--|

| Input    | Output |  |

| 0        | 1      |  |

| 1        | 0      |  |

| 71.      | 71.    |  |

| A         | AND gate  |        |  |

|-----------|-----------|--------|--|

| Inputs    |           | Output |  |

| <i>I1</i> | <i>I2</i> |        |  |

| 0         | 0         | 0      |  |

| 0         | 1         | 0      |  |

| 0         | u         | 0      |  |

| u         | 0         | 0      |  |

| u         | 1         | u      |  |

| u         | u         | u      |  |

| 1         | 0         | 0      |  |

| 1         | 1         | 1      |  |

| 1         | u         | u      |  |

| OR gate   |           |        |  |

|-----------|-----------|--------|--|

| Inputs    |           | Output |  |

| <i>I1</i> | <i>I2</i> |        |  |

| 0         | 0         | 0      |  |

| 0         | 1         | 1      |  |

| 0         | u         | u      |  |

| u         | 0         | u      |  |

| u         | 1         | 1      |  |

| u         | u         | u      |  |

| 1         | 0         | 1      |  |

| 1         | 1         | 1      |  |

| 1         | u         | 1      |  |

Table 3.1: Definition of behavior of basic gates.

Introduction of delays and undefined signals bring to life a number of questions not present in the case of ideal (time independent) boolean circuits. We need to know for instance, how these  $\delta$ 's can be computed, how we can guarantee that a particular circuit computes g with a given  $\delta$ , how we can check if a component of a circuit can be replaced by a similar component with a smaller/bigger delay without violating some important properties of the circuit, etc. To answer these and similar questions we need to have a precise description of the behavior of a circuit, which, given a vector of

values applied to its input wires, will determine the values of signals present on every wire of the circuit at any moment of time. In the next section we design and implement a program in A-Prolog which does exactly that. One of the main advantages of using A-Prolog is that the program is very concise, clear, and elaboration tolerant. More importantly, in subsequent sections, we demonstrate that the expressive power of A-Prolog also allows for the description of a variety of tasks, e.g. computing maximum delay of a circuit and detection of glitches.

## 3.3 Formalizing Digital Circuits in A-Prolog

We start by introducing a simple language  $\mathcal{L}_{ckt}$  for describing digital circuits. The language has four types of object constants (names for objects of the domain):

- (a)  $g_1, g_2 \dots$  for gates;

- (b)  $w_1, w_2, \ldots$  for wires;

- (c) 0, 1, u for signals;

- (d) and\_gate, or\_gate, not\_gate for the three basic gate types we chose to represent.

Variables for gates, wires, and signals will be denoted by possibly indexed letters G, W, and S, respectively. We also assume that  $\mathcal{L}_{ckt}$  contains standard notation for numbers, needed to denote delays. To describe the geometry of the circuit we use statements of the form output(W, G) and input(W, G) read as "W is an output (input)

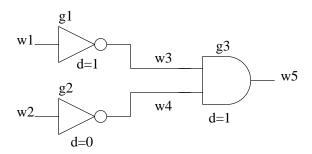

wire of gate G." The types of gates in the circuit and the gates' delays are expressed by the statements  $type\_of(G, gate\_type)$  (G is of type  $gate\_type$ ) and delay(G, D) (G has delay D). In this notation, the circuit from Figure 3.3 corresponds to the following collection of statements of A-Prolog:

Figure 3.3: Graphical representation of a digital circuit.

```

type\_of(g_1, not\_gate).

type\_of(g_2, not\_gate).

type\_of(g_3, and\_gate).

delay(g_1, 1).

delay(g_2, 0).

delay(g_3, 1).

input(w_1, g_1).

input(w_2, g_2).

input(w_3, g_3).

input(w_4, g_3).

output(w_4, g_2).

output(w_4, g_2).

output(w_5, g_3).

```

We denote such a representation of a circuit C by  $\pi(C)$ .

To describe the dynamic behavior of the circuit we need to introduce the notion of time. AI researchers developed a large variety of different models of time. For our purposes, we assume the discrete linear time model in which time is represented by non-negative integers. We view the application of signals to the input wires of a circuit as the execution of an action which changes the previous signals on these wires. This triggers a process of signal propagation through the circuit which goes uninterrupted unless the input signals are changed again. In this way, describing the behavior of the circuit can be reduced to specifying effects of the corresponding actions as it is done in action theories of AI (see for instance [77, 124, 132, 162, 172, 194]). In these theories, dynamic domains consist of actions and fluents (properties whose values depend on time). Action theories are built to specify the values of fluents at an arbitrary moment t, given their values at moment 0 and the domain history (a sequence of actions performed in the domain in the past). In our domain we have only one (parameterized) action apply(w,s) and one (parameterized) propositional fluent, value(w, s). A statement occurs(apply(w, s), t) says that at moment t signal s is applied to wire w, while a statement holds(value(w,s),t) denotes that at moment t the value of the signal on wire w is s. We will also use an auxiliary relation  $opposite(s_1, s_2)$  satisfied by the pairs [0, 1], [1, 0] and [u, u], where u corresponds to undefined values between 0 and 1. Direct effects of actions will be represented in A-Prolog by the following rule:

$$holds(value(W, S), T + 1) \leftarrow occurs(apply(W, S), T).$$

(3.1)

Here T is a variable for time. To guarantee the computability of our models we assume that T ranges between 0 and some fixed time denoted by the constant last time. (This constant can be viewed as a parameter of our system and it is entered by the user via the entry program as a part of the problem instance.) The next rule describes the propagation of the applied signal through the NOT gate of the circuit.

$$holds(value(W_2, S_2), T + D) \leftarrow type\_of(G, not\_gate),$$

$$delay(G, D),$$

$$input(W_1, G),$$

$$output(W_2, G),$$

$$opposite(S_1, S_2),$$

$$holds(value(W_1, S_1), T).$$

Auxiliary predicate opposite(S, S') is used only for conciseness of representation. It can be eliminated, in which case there would be three such rules to represent the propagation of a signal through a gate NOT, instead of the single rule above.

To represent the function of gates AND and OR, we need to define some auxiliary relations. The first relation,  $not\_all\_inputs(G, S, T)$ , holds if at moment T some input wire of the gate G has a signal different from S. This can be expressed by the following rule:

$$not\_all\_inputs(G, S_1, T) \leftarrow input(W, G),$$

$$S_1 \neq S_2,$$

$$holds(value(W, S_2), T).$$

The second relation,  $all\_inputs(G, S, T)$ , holds if at time T all the input wires of G have value S, and is defined by the rule:

$$all\_inputs(G, S, T) \leftarrow not\ not\_all\_inputs(G, S, T).$$

Finally, the relation  $contains\_input(G, S, T)$  holds if at moment T at least one input wire of G has value S, and is defined by the rule:

$$contains\_input(G, S, T) \leftarrow input(W, G),$$

$$holds(value(W, S), T).$$

Now we can define the propagation of signals through AND gates:

$$holds(value(W, 1), T + D) \leftarrow type\_of(G, and\_gate),$$

$$delay(G, D),$$

$$output(W, G),$$

$$all\_inputs(G, 1, T).$$

$$holds(value(W, 0), T + D) \leftarrow type\_of(G, and\_gate),$$

$$delay(G, D),$$

$$output(W, G),$$

$$contains\_input(G, 0, T).$$

$$holds(value(W, u), T + D) \leftarrow type\_of(G, and\_gate),$$

$$delay(G, D),$$

$$output(W, G),$$

$$not\ contains\_input(G, 0, T),$$

$$contains\_input(G, u, T).$$

The rules for propagation of signals through OR gates are defined next.

$$\begin{aligned} holds(value(W,0),T+D) & \leftarrow & type\_of(G,or\_gate), \\ & & delay(G,D), \\ & & output(W,G), \\ & & all\_inputs(G,0,T). \end{aligned}$$

$$\begin{aligned} holds(value(W,1),T+D) & \leftarrow & type\_of(G,or\_gate), \\ & & delay(G,D), \\ & & output(W,G), \\ & & contains\_input(G,1,T). \end{aligned}$$

$$\begin{aligned} holds(value(W,u),T+D) &\leftarrow type\_of(G,or\_gate), \\ &\quad delay(G,D), \\ &\quad output(W,G), \\ &\quad not\; contains\_input(G,1,T), \\ &\quad contains\_input(G,u,T). \end{aligned}$$

All the above rules define the effects of changes caused in the circuit by applying new signals to its input wires. To complete our program we need to specify when the values of fluents do not change. The task of finding a compact way to specify this in a formal language is called the *frame problem*. J. McCarthy in [138] suggested that this problem is closely related to the problem of representing a particular default called the *law of inertia*. The law says that "normally, things stay as they are," i.e., in dynamic domains fluents do not change their values unless they are forced to. Fortunately, the methodology of representing defaults in A-Prolog is now well understood and can be applied to obtain a simple and natural solution to the frame problem for our domain.

The solution is given by the next two rules.

The first of them is the Law of Inertia:

$$holds(value(W, S), T+1) \leftarrow holds(value(W, S), T),$$

$not \neg holds(value(W, S), T+1).$

This rule allows the reasoner (the program) to assume that the value of a signal on a wire W does not change from one moment to the next, unless it is forced to believe otherwise. The second rule states that there may be at most one signal present on a wire at a given moment of time:

$$\neg holds(value(W, S_1), T) \leftarrow S_1 \neq S_2,$$

$holds(value(W, S_2), T).$

Rules of this sort are often called "state constraints". They play an important role in theory of action languages and are mainly responsible for the conciseness of the representation of indirect effects of actions.